6,000 个 RISC-V 内核的“芯片”

泉源:内容由半导体行业观看(ID:icbank)编译自「tomshardware」,感谢。

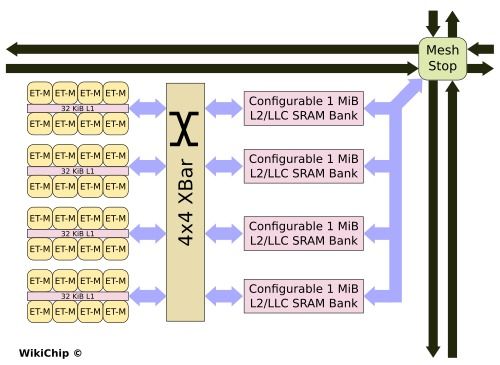

通过将 6,000 个 RISC-V SERV 内核与赛灵思最壮大的 FPGA 设计之一 的VCU128 板配对开辟,开放度者实现了RISC-V 内核最麋集分列的新天下记录(由CoreScore 基准测试丈量)。该基准测试模仿了可以在单片硅片上摆设几多个 SERV 内核,而赛灵思的 Virtex UltraScale+ VCU128 FPGA通过其内部重新设置装备摆设可以容纳多达 6,000 个 SERV 内核。之前的记载连结者共有 5,087 个内核托管在 Xilinx 的 VCU118 上。

FPGA(现场可编程门阵列)是一种奇怪的硬件,由于它们具有很少的牢固功效元件。相反,它们被构建为可以在运行中(或在现场)编程,仿照步伐员界说的晶体管分列。这根本上许可 FPGA 成为我们最靠近自顺应处置惩罚电子设置装备摆设的产物,依据手头的事情负载随时改变(这是一个简化的解说)。

“当您拥有屡获殊荣的 SERV,天下上最小的 RISC-V CPU 时,您会做什么?” SERV 焦点和 CoreScore 基准测试的设计者 Olof Kindgren 问道。“嗯,除此之外,我们固然想看看您可以在种种设置装备摆设中安置几多个 SERV 内核。这便是 CoreScore 的用途。在现在 30 块板的列表中,我们如今可以找到 Sylvain Lefebvre以及得当 6000 个 SERV 内核的 Xilinx VCU128 板。”

这些内核不是您通常在Intel 或 AMD 的最佳游戏 CPU上找到的内核;它们是精简的、准体系的位串行事情单位,包罗尽大概少的无关功效。这种要领最大限度地淘汰了每个内核占用的总芯片空间。该设计通过事情负载并行化来实现性能,而不是来自每个焦点的显着处置惩罚。

“我们正在靠近最大值,”Lefebvre 在谈到他的 6,000 核记载时说,“利用 VCU128 FPGA 的 98.5% LUT [查找表](和 100% BRAM [块 RAM])。与 Olof Kindgren 互助非常有味在这一点上,这是对我们 Xilinx VCU128 的完善先容。”

附:原文

A new world record for the densest arrangement of RISC-V cores (measured by the CoreScore benchmark) has been achieved by pairing 6,000 RISC-V SERV cores and one of Xilinx's most powerful FPGA designs, the VCU128 board. The benchmark simulates how many SERV cores can be deployed on a single piece of silicon, and the Xilinx's Virtex UltraScale+ VCU128 FPGA can fit as many as 6,000 SERV cores via its internal reconfiguration. The previous record-holder had a total of 5,087 cores hosted on Xilinx's VCU118.

FPGAs (Field-Programmable Gate Array) are exotic pieces of hardware because they have very few fixed-function elements. Instead, they are built to be programmable on the fly (or in the field), mimicking transistor arrangements defined by the programmer. This essentially allows FPGAs to be the closest we have to adaptive processing electronics, changing from moment to moment according to the workload at hand (this is a simplified explanation).

"What do you do when you have the award-winning SERV, the world's smallest RISC-V CPU?" asks Olof Kindgren, designer of both the SERV core and the CoreScore benchmark. "Well, among other things, we, of course, want to see how many SERV cores you can fit into various devices. This is what CoreScore is for. And on top of that list of currently 30 boards, we can now find Sylvain Lefebvre and his Xilinx VCU128 board that fits 6000 SERV cores."

These cores aren't what you'd typically find on your best CPUs for gaming from Intel or AMD; they are stripped-down, barebones bit-serial work units that include as few extraneous functions as possible. That approach minimizes the total die space occupied by each core. The design achieves performance via workload parallelization, not from the obvious processing grunt from each core.

"We are nearing the max," Lefebvre says of his 6,000-core record, "with 98.5% LUTs [Lookup Tables] (and 100% BRAM [Block RAM]) of the VCU128 FPGA utilized. It's been great fun working with Olof Kindgren on this, and it was a perfect intro to our Xilinx VCU128 monster."

★ 点击文末【阅读原文】,可检察本文原文链接!

*免责声明:本文由作者原创。文章内容系作者小我私家看法,半导体行业观看转载仅为了转达一种差别的看法,不代表半导体行业观看对该看法赞许或支持,假如有任何贰言,接待联络半导体行业观看。

今日是《半导体行业观看》为您分享的第2812内容,接待存眷。

晶圆|集成电路|设置装备摆设|汽车芯片|存储|台积电|AI|封装

原文链接!