从Intel做了个RISC-V处置惩罚器谈起

媒介

克日从Intel传来消息,Intel FPGA大将推出新一代的Nios软核处置惩罚器Nios V。该软核处置惩罚器采纳现在被遍及存眷的RISC-V开源指令集,将在Quartus Prime Pro Edition 21.3版本中显现。

那什么是软核处置惩罚器?在FPGA中为什么必要利用软核处置惩罚器?软核处置惩罚器在FPGA中历经了如何的进展进程?为什么厥后Intel(Altera)和Xilinx都推出了基于Arm硬核处置惩罚器的SoC-FPGA?如今的FPGA中软核处置惩罚器是否另有用武之地?Intel此时推出访用RISC-V指令集的软核有何用意?对RISC-V指令集的远景有何影响?

本篇文章将实验答复以上题目,因为时间匆匆加上作者程度有限,部门信息泉源自网络消息。若有漏掉或错误,接待家人们留言指正。

1.客从那边来——FPGA中软核处置惩罚器的进展史

FPGA中利用软核的汗青已经很永劫间了,2000年开始Altera和Xilinx就分别推出了Nios和MicroBlaze这两种软核。到了2004年Altera推出了32位全新架构的Nios-II,而Xilinx也进一步推出了8位的PicoBlaze。至此,软核处置惩罚器及其开辟东西作为FPGA产物中一个紧张的谱系登上了汗青舞台。

那么为什么FPGA中必要利用软核处置惩罚器呢?实在这是由两方面身分配合决定的。主要的身分还说要归结于摩尔定律的作用导致FPGA容量的连续提拔。到2000年左右,FPGA已经过早期只能做简洁规律的粘合器件进展为可以承载某个要害子体系的大范围规律器件。FPGA容量的增添使得在FPGA中使用查找表等可编程规律实现一个处置惩罚器不再是一件非常奢侈的事变。别的一方面的身分照旧处置惩罚器自己所具备利用简洁、操纵机动、易于开辟的上风,让处置惩罚器在实现操纵、决议计划类使命时有非常大的上风。

假如我们不在FPGA中利用软核处置惩罚器,那么对付这些操纵、决议计划类使命要么必要自主构建一个庞大状态机来完成,要么必要分外在FPGA外部“外挂”一个小单片机来完成。这一类使命的特点是利用并不频仍,但流程、步调较为繁琐。比方对付许多IP核在事情之前要对其举行一些初始化设置装备摆设,又好比与FPGA共同的外围模仿、存储器等芯片的参数在某些时间必要简洁的调治,FPGA实现运算历程中有部门操纵必要弃取等等。

状态机无疑是数字体系中最要害也最难设计的子模块。庞大状态机的设计不光难还简单堕落,一旦显现设计缺陷要准时改正也黑白常困难的。而处置惩罚器则纷歧样,处置惩罚器是一种颠末多次验证确保精确的子体系,并且有非常成熟的Debug方法。利用处置惩罚器来实现对规律电路的初始化和状态操纵,其难度要远远小于设计多个庞大状态机。是以,当FPGA的容量支持在实现了焦点功效以外再增添一个处置惩罚器来作为帮助的时间,在FPGA中去嵌入一个处置惩罚器就变得非常的天然。

但在今后无论是Nios-II照旧MicroBlaze进展的并不顺遂,广阔工程师们对软核处置惩罚器的诉苦并一向不停。这此中的细致题目我们可以鄙人一节详细阐发。随着Xilinx在2010年公布Zynq系列以Arm硬核结构的新一代SoC-FPGA,FPGA与处置惩罚器融合风头被嵌入Arm高端硬核处置惩罚器所抢走并恒久据有人们的视线,而软核好像被忘记到了角落里。

但究竟上软核并非没有进一步的进展。Altera以及厥后的Intel一向不停的在对Nios II举行升级改革,在厥后乃至融入了多核、片上彀络等高端处置惩罚器本领备的特性。而Xilinx则在不停的富厚软核的生态,把一些MCU级另外处置惩罚器不停的结构成软核。其最新的一次“紧张”希望是与Arm Design Start打算互助,将Arm的Cortex-M1核Cotex-M3版本的处置惩罚器核深度的整合到本身的东西链中。而随着Nios V的公布,评释软核处置惩罚器依旧有着它奇特的作用和壮大的生命力。

2.“软”之殇——软核处置惩罚器一向不尴不尬的缘故原由

软核处置惩罚器固然显现比力久,但其一向处于不尴不尬的职位地方。究其缘故原由无非性能、生态两部门的身分。

起首说性能,软核处置惩罚器是寄托FPGA内部资源结构的,以查找表、嵌入式乘法器、可编程互连线注定无法结构出高性能的处置惩罚器。假如对付处置惩罚器微架构自己不加以优化,纵然在“高端”FPGA中也只能跑到不敷100Mhz的时钟频率。在举行了深度优化今后,这个频率也许能到150Mhz-200Mhz,而在添加了外设今后再举行团体的结构布线,时钟频率很大概又失下去了。

实在跑到100Mhz出头如许一个频率的确相称的难堪。假如当MCU用呢,这个频率应该是够了。但题目是我换一块小容量点的FPGA然后再把节省出来的钱分外买一个廉价的MCU不可吗?假如是把软核处置惩罚器真确当“处置惩罚器”看,这点性能又真的有点“不敷看”的。当年笔者在到场Altera金牌讲师培训的时间就这个题目和Altera的AE深入商议过,AE给的回复是“不要为了用软核而去用软核”,这现实上照旧没有真正答复题目。

面临性能不敷的情形,Altera接纳的方法是不停去增强和优化,但是FPGA自己的布局决定了再怎么优化其性能上限也是有限的。而让软核“多核化”更是有点“刻舟求剑”的意思。而Xilinx好像要越发“硬派”一些,对付性能不敷的情形Xilinx给的方法便是“上硬核”。只是Xilinx早期一向受通讯行业影响太深,利用的硬核是在通讯行业很盛行但在另外行业比力“非主流”的PowerPC。而直到Xilinx“想通了”开始集成Arm处置惩罚器今后,整个处置惩罚器+FPGA软硬件融合的市场才被引爆。

和性能不敷相对,生态太差是导致软核处置惩罚器一向不火的别的一个推手。实在但凡涉及处处理器必谈生态。由于处置惩罚器不是一般的数字规律电路,没有整个软件东西链为焦点的生态情况支持,处置惩罚器是搞不起来的。无论是Nios II照旧MicroBlaze,其素质都是在“自建生态”。那也必定是要面对生态竞争的题目。随着Arm在嵌入式范畴的一家独大,雷同MIPS如许的专业处置惩罚器公司都被竞争下去了,更况且两大FPGA公司如许的兼职玩家。

生态不可就意味着利用的人少,意味着提出的题目找不到人商议,意味着没有许多现成的案例可以参考、进修、移植。这反过来又导致用的人更少。固然软核属于“深度嵌入”应用,普通是步伐开辟者直面硬件举行编程,软件栈的深度浅。但如许一样要碰到以上题目。这便是在许多情形下,假如有的选择开辟者甘心在FPGA表面外挂一个小封装的单片机来完成软核的功效,也只管即便少去碰软核。由于利用软核来举行开辟的履历着实是让人觉得太难过了。

3.路在何方——Intel开辟RISC-V指令集软核处置惩罚器的缘故原由浅析

实在在两年前我就写过一篇商议RISC-V现在得当的市场的文章:

http://zhuanlan.zhihu.com/p/54778540

此中提出“用户不行见处置惩罚器”市场是RISC-V必定会占据,并且Arm没有什么上风的市场。此中也举例阐明了NVIDIA要用基于RISC-V的处置惩罚器替换的本来自有指令的Falcon。实在FPGA中的软核黑白常切合“用户不行见处置惩罚器”这个场景的。软核自己便是FPGA中替换庞大状态机而存在的,运行预先设定好的软件,普通情形下不必要用户对其编程。是以做RISC-V指令集的软核处置惩罚器从市场层面是可行的。

从技能层面说,RISC-V指令集采纳告终构化的指令集界说方法。其特点黑白常便利的实现指令的裁剪核扩展。而FPGA恰好便是一个非常得当于指令集裁剪/扩展的范畴。因为FPGA的可编程特性,利用充足的资源就可以搭建出实现恣意指令的软核处置惩罚器。而FPGA针对差别应用的定制性很强,对付指令的需求实在不是那么的大而全。针对特定的应用,定制符合的指令,终极以最小的分外开销实现了帮助功效。这才是软核处置惩罚器真正精确的用途。Nios II系列本来是有很好的指令定制的机制的,但在已往一向没有发挥出应有的成效。而这一次Nios V的公布有望联合RISC-V指令集特有的技能上风在这一点上实现突破。

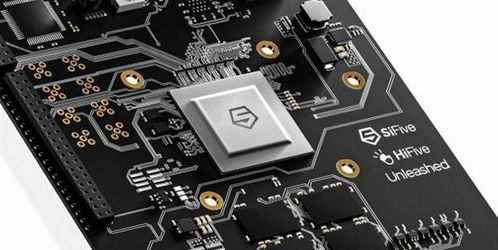

而从计谋层面上来说,随着Arm和NVIDIA的归并历程不停推进。Intel和Arm的干系正在从玄妙走向诡异。Intel对付RISC-V指令集也是“觊觎已久”。在8月份的时间还传出过Intel要收购基于RISC-V指令集的处置惩罚器IP提供商SiFive的听说。固然最终听说被证明不实,但空穴来风必有泉源。而此时推出基于RISC-V指令集的软核未尝不是一种计谋摆设。假如再大胆假想一下,Intel将来是否会推出RISC-V指令集硬核处置惩罚器的SoC-FPGA实在也未可知。

4.小结

不管怎么说,Intel对付Nios的改造便是软核处置惩罚器范畴的一次厘革,又是RISC-V指令集取得的又一紧张希望。将来在嵌入式范畴,RISC-V指令集的影响力还会连续加强。

END

作者简介

黄乐天,电子科技大学电子科学与工程学院,副传授, 电子科技大学博士。重要研究偏向为盘算机体系架构与体系级芯片设计、多芯粒集成微体系,已在IEEE Transactions on Computers (CCF A 类期刊)等高程度期刊和CODE+ISSS、FCCM、ASPDAC、ISCAS等顶级集会上颁发高程度论文50 余篇,申请专利30余项,出书著作《FPGA异构盘算》1部。到场事情以来主持和参加过国度级重点科研项目多项。曾荣获Altera公司(Intel PSG)金牌培训师、 第七、第八、第十二届研究生电子设计大赛优异引导西席、电子科大网络名师等称呼。

*免责声明:本文由作者原创。文章内容系作者小我私家看法,半导体行业观看转载仅为了转达一种差别的看法,不代表半导体行业观看对该看法赞许或支持,假如有任何贰言,接待联络半导体行业观看。

今日是《半导体行业观看》为您分享的第2815内容,接待存眷。

晶圆|集成电路|设置装备摆设|汽车芯片|存储|台积电|AI|封装