FPGA开辟板为什么要利用SDRAM

SDRAM有一个同步接口,在相应操纵输入前会等候一个时钟信号,如许就能和盘算机的体系总线 同步。时钟被用来驱动一个有限状态机,对进入的指令举行管线(Pipeline)操纵。这使得SDRAM与没有同步接口的异步DRAM相比,可以有一个更庞大的操纵模式。

管线 意味着芯片可以在处置惩罚完之前的指令前,担当一个新的指令 。在一个写入的管线 中,写入下令在另一个指令实行完之后可以连忙实行,而不必要等候数据写入存储行列步队的时间。在一个读取的流水线中,必要的数据 在读取指令发出之后牢固数目的时钟频率后到达,而这个等候的历程可以发出别的附加指令。这种耽误被称为等候时间(Latency),在为盘算机购置内存时是一个很紧张的参数。

SDRAM在盘算机中被遍及利用,从早先的SDRAM到之后一代的DDR(或称DDR1),然后是DDR2 和DDR3 进入大众市场,2015年开始DDR4进入消耗市场。如UMI型号 UD408G5S1AF的一款8Gb 32位 DDR4 SDRAM,是一款支持利用在英特尔Arria 10 SoC FPGA以及Kintex Ultrascale FPGA中的存储器。32位 DDR4 SDRAM非常得当边沿类盘算,或对PCB面积有紧凑要求的深度进修盘算设置装备摆设。英尚微支持32位DDR4 SDRAM送样及测试.

为什么要利用内存操纵器?

动态内存的驱动比静态内存的驱动越发庞大...我们必要行,列和存储体以及革新周期来处置惩罚。但是因为SDRAM的高速性和低单元本钱使其惹人注目。

是以我们必要的是一种访问SDRAM的要领,但是要易于利用静态内存。这便是创建内存操纵器的缘故原由。它们充任转换层:一方面,它们为用户提供了易于利用的内存接口,然落伍行了繁琐的事情来驱动真实的SDRAM信号。

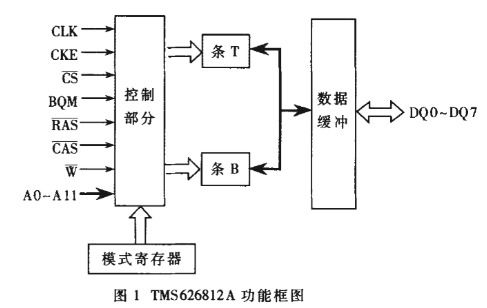

SDRAM引脚

假如我们看一下SDRAM的引脚,那么会有一些新来者。

SDRAM引脚

地点和数据总线仍旧存在,但是地点总线只有11位(用于提供要打开的行,然后提供列地点)。BA引脚指定了存储区(因为在我们的示例中只有2个存储区,是以我们仅必要一个引脚)。WE,CAS和RAS一路用作下令引脚,是以我们可以向SDRAM发送8个差别的下令(下令包罗“打开行”,“读取”,“写入”和“封闭行”)。利用了其他一些引脚(但未在图片上表现),比方时钟,片选,字节使能...

请细致,在动态内存中,“打开行”称为激活,“封闭行”称为预充电。

革新

SDRAM是动态存储器:因为每个存储器位值(0或1)都储存在一个微小的电容器中,电荷随时间衰减,是以必要定期革新其内容。但是衰减率充足低,只要定期对其举行读取和重新写入(“革新”),制造商就可以包管不会丢失任何数据。

有两种革新机制

· FPGA将“主动革新”下令发送到SDRAM。

只要确保它定期完成(SDRAM数据表会报告您最小革新频率)。

· FPGA“每每”访问每一行。

打开一行会导致SDRAM中的“感测放大器”得到该行全部电容器电荷的副本。然后,当该行封闭时,较早检测到的值将被复制回电容器中,从而革新历程中的数据。