疑号链:阻抗立室

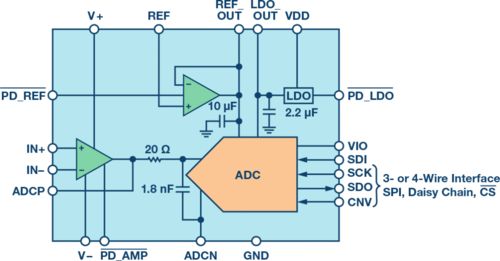

射频信号链通常包罗一系列射频设置装备摆设和组件,各个设置装备摆设和组件具有自身的奇特举动。

射频收发框

但是,在任何情形下,信号链中的各个组件和设置装备摆设会在其输入端口和输出端口引起阻抗。别的,信号链中的设置装备摆设与组件之间互连也会引起其自身的阻抗。假定任何端口上的阻抗是电流/电压之比,则组件或设置装备摆设的内部相应会直接影响信号链中每个元件端口处阻抗。今日就一路相识一下阻抗立室以及在射频信号链中的紧张性。

(一)根本界说

阻抗:

具有电阻、电感和电容的电路里,对交换电所起的拦阻作用叫做阻抗。阻抗常用Z表现。阻抗由电阻、感抗和容抗三者构成,但不是三者简洁相加。假如三者是串联的,又知道交换电的频率f、电阻R、电感L和电容C,那么串联电路的阻抗。阻抗的单元是欧。

对付一个详细电路,阻抗不是稳定的,而是随着频率改变而改变。在电阻、电感和电容串联电路中,电路的阻抗普通来说比电阻大。也便是阻抗减小到最小值。在电感和电容并联电路中,谐振的时间阻抗增添到最大值,这和串联电路相反。

阻抗立室:

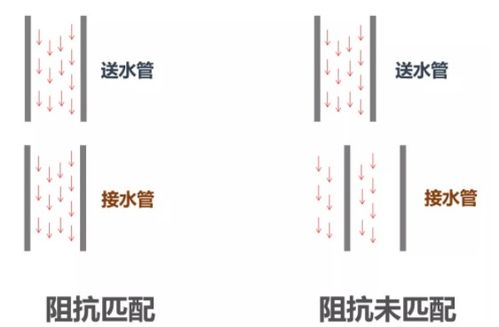

阻抗立室(Impedance matching)是微波电子学里的一部门,在高频设计中是一个常用的观点,重要用于传输线上, 重要用于传输线上,以此来到达全部高频的微波信号均能通报至负载点的目标,并且险些不会有信号反射返来源点,从而提拔能源效益。信号源内阻与所接传输线的特性阻抗巨细相称且相位雷同,或传输线的特性阻抗与所接负载阻抗的巨细相称且相位雷同,分别称为传输线的输入端或输出端处于阻抗立室状态,简称为阻抗立室。

(二)阻抗立室的紧张性

在射频信号链中,阻抗立室具有更紧张的意义。阻抗立室的目标是为相识决功率传输时阻抗不立室的题目。在射频信号链的每个节点上,假如阻抗立室禁绝确,会孕育发生反射。丈量阻抗不立室的一种常用要领是通过所得驻波比(SWR)或电压驻波比(VSWR)举行表现。是以很多常见的射频组件和设置装备摆设的端口阻抗设计为50 Ohm或75 Ohm,如许可以最大水平地淘汰阻抗不立室的大概性,并低落必要设计职员确保信号链中每个元件之间阻抗立室的要求。

信号链中显现阻抗不立室会孕育发生种种不良影响。直接体现为本应沿信号链传输的某些信号强度会因阻抗不立室被反射。这会导致信号强度降落,并使信号链中显现衰减。别的,反射信号可以在两个不立室的端口之间来回“反弹”并孕育发生驻波。该驻波大概会像端口上的直流电压一样侵害或转变某些射频组件和设置装备摆设的举动。思量到射频电路通常为非线性,反射信号也有大概导致信号链的通带中孕育发生杂散、谐波、噪声以及其他不良的信号劣化。

在极度情形下,阻抗不立室大概会导致因反射信号过强而破坏信号链中的设置装备摆设和组件。比方,假如高功率放射机的输出端与天线端口不立室,则反射信号强度大概会破坏高功率放大器(HPA),而高功率放大器比力昂贵,且修理起来比力庞大。

(三)阻抗立室的办理方案

在某些情形下,信号链内的阻抗不立室险些无法幸免。比方,某些范例的滤波器素质上具有反射性。这意味着滤波器通带之外的频率内容将会显现阻抗不立室,导致通带之外的那些信号被反射。滤波器通常安排在混频器、振荡器、放射机和其他有源元件的输出端,是以大概导致滤波器、元件或信号质量降落和受损。为相识决这个题目,可以采纳其他范例的滤波器,比方汲取滤波器,该滤波器重要汲取通带之外的射频能量,大概在信号链的反射元件之间安排衰减器,以汲取反射信号的能量并防备孕育发生驻波。

在某些必要将阻抗不立室引起的反射降到最小、实现最大功率传输或服从其他限定(比方将吸收信号中的噪声含量降到最小)的情形下,大概必要阻抗立室电路。从素质上来说,阻抗立室电路可以举行此中一个端口到另一个端口的阻抗变更。假如此阻抗变更旨在实现最大功率传输,则阻抗立室会将源端口和负载端口变更为相互共轭立室。在将天线端口与吸收机输入端(比方低噪声放大器(LNA))举行立室的情形下,可以采纳差别的要领。假如必要思量噪声,则将大概不会采纳阻抗立室电路举行共轭立室,而是采纳阻抗立室网络,其旨在提供低噪声放大器的噪声系数优化源电阻和偏置点。